[筆記] 數位系統設計與實驗 DSDL 2014/02/27

各種 GATE

NOT

AND

OR

NAND

NOR

XOR

NXOR

X * 1 = X

X + 1 = 1

X * 0 = 0

(X * Y * ...)' = X'+Y' + ...

證明下式

(X * Y) + (Y * Z) + (X' * Z) = X * Y + X' * Z

pf:

原式 = (X * Y) + (1)*(Y * Z) + (X' * Z)

=> (X * Y) + (X' + X)(Y * Z) + (X' * Z)

=>

A B Cin | Cout S

0 0 0 | 0 0

0 0 1 | 0 1

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 1

將上表整理成sum of product canonical form

S = A'B'Cin + A'BCin' + AB'Cin' + ABCin

Cout = A'BCin + AB'Cin + ABCin' + ABCin

A B C | F F'

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 0

將上表整理成sum of product canonical form

(要看1的位置)

F = A'B'C + A'BC + AB'C + ABC' + ABC

A B C | F F'

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 0

A B C | F F'

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 0

將上表整理成product of sum canonical form

(要看0的位置)

F = (A + B + C)(A + B' + C)(A' + B + C)

...見鬼了!why?

因為~

由第一行推可知 原本 F' = A'B'C' 迪摩根定理說 (F')' = (A'B'C')' = (A')'+ (B')' + (C')' = A + B + C 得證!

A B | F

0 0 | 1

0 1 | 0

1 0 | 1

1 1 | 0

F = A'B' + AB'

= B'(A+A')

= B'(1)

= B'

0 1 A

0 | 1 | 1 |

1 | 0 | 0 |

B

將上排 1 1 圈起來,A 上面的結果 0 1 抵消掉,可知簡化後為 B'

同理,

例2 :

A B | F

0 0 | 1

0 1 | 1

1 0 | 0

1 1 | 0

0 1 A

0 | 1 | 0 |

1 | 1 | 0 |

B

將上排 1 1 圈起來,B 上面的結果 0 1 抵消掉,可知簡化後為 A'

===============================

例3 :

A B | F

0 0 | 0

0 1 | 0

1 0 | 1

1 1 | 1

0 1 A

0 | 0 | 1 |

1 | 0 | 1 |

B

將上排 1 1 圈起來,B 上面的結果 0 1 抵消掉,可知簡化後為 A

===============================

例4 :

下面這條圈起來卷簡化之後是 CD = 10 --> CD'

這次多圈一點,發現簡化後得到 C = 1 --> C

這兩個簡化結果為 A'BD

角落的四個也可以圈起來一起簡化,結果為--> B'D'

全部簡化完,最後的結果得到: B'D' + A'BD + C

========================================

符號:

XOR ^

AND &

OR |

AND 的優先權 > OR

應用:

X Y Z 三個 bit 的sum如何做?

X ^ Y ^ Z

NOT

AND

OR

NAND

NOR

XOR

NXOR

Boolean algebra

X + 0 = XX * 1 = X

X + 1 = 1

X * 0 = 0

de Morgan's

(X + Y + ...)' = X' * Y' * ...(X * Y * ...)' = X'+Y' + ...

證明下式

(X * Y) + (Y * Z) + (X' * Z) = X * Y + X' * Z

pf:

原式 = (X * Y) + (1)*(Y * Z) + (X' * Z)

=> (X * Y) + (X' + X)(Y * Z) + (X' * Z)

=>

A B Cin | Cout S

0 0 0 | 0 0

0 0 1 | 0 1

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 1

將上表整理成sum of product canonical form

S = A'B'Cin + A'BCin' + AB'Cin' + ABCin

Cout = A'BCin + AB'Cin + ABCin' + ABCin

A B C | F F'

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 0

將上表整理成sum of product canonical form

(要看1的位置)

F = A'B'C + A'BC + AB'C + ABC' + ABC

A B C | F F'

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 0

A B C | F F'

0 0 0 | 0 1

0 0 1 | 1 0

0 1 0 | 0 1

0 1 1 | 1 0

1 0 0 | 0 1

1 0 1 | 1 0

1 1 0 | 1 0

1 1 1 | 1 0

將上表整理成product of sum canonical form

(要看0的位置)

F = (A + B + C)(A + B' + C)(A' + B + C)

...見鬼了!why?

因為~

由第一行推可知 原本 F' = A'B'C' 迪摩根定理說 (F')' = (A'B'C')' = (A')'+ (B')' + (C')' = A + B + C 得證!

化簡方法 -- 使用 Karnaugh map

例:A B | F

0 0 | 1

0 1 | 0

1 0 | 1

1 1 | 0

F = A'B' + AB'

= B'(A+A')

= B'(1)

= B'

0 1 A

0 | 1 | 1 |

1 | 0 | 0 |

B

將上排 1 1 圈起來,A 上面的結果 0 1 抵消掉,可知簡化後為 B'

同理,

例2 :

A B | F

0 0 | 1

0 1 | 1

1 0 | 0

1 1 | 0

0 1 A

0 | 1 | 0 |

1 | 1 | 0 |

B

將上排 1 1 圈起來,B 上面的結果 0 1 抵消掉,可知簡化後為 A'

===============================

例3 :

A B | F

0 0 | 0

0 1 | 0

1 0 | 1

1 1 | 1

0 1 A

0 | 0 | 1 |

1 | 0 | 1 |

B

將上排 1 1 圈起來,B 上面的結果 0 1 抵消掉,可知簡化後為 A

===============================

例4 :

|

CD\AB

|

00

|

01

|

11

|

10

|

|

00

|

1

|

0

|

0

|

1

|

|

01

|

0

|

1

|

0

|

0

|

|

11

|

1

|

1

|

1

|

1

|

|

10

|

1

|

1

|

1

|

1

|

F (A,B,C,D) = Σm (0, 2, 3, 5, 6, 7, 8, 10, 11, 14,

15)

下面這條圈起來卷簡化之後是 CD = 10 --> CD'

這次多圈一點,發現簡化後得到 C = 1 --> C

這兩個簡化結果為 A'BD

角落的四個也可以圈起來一起簡化,結果為--> B'D'

全部簡化完,最後的結果得到: B'D' + A'BD + C

========================================

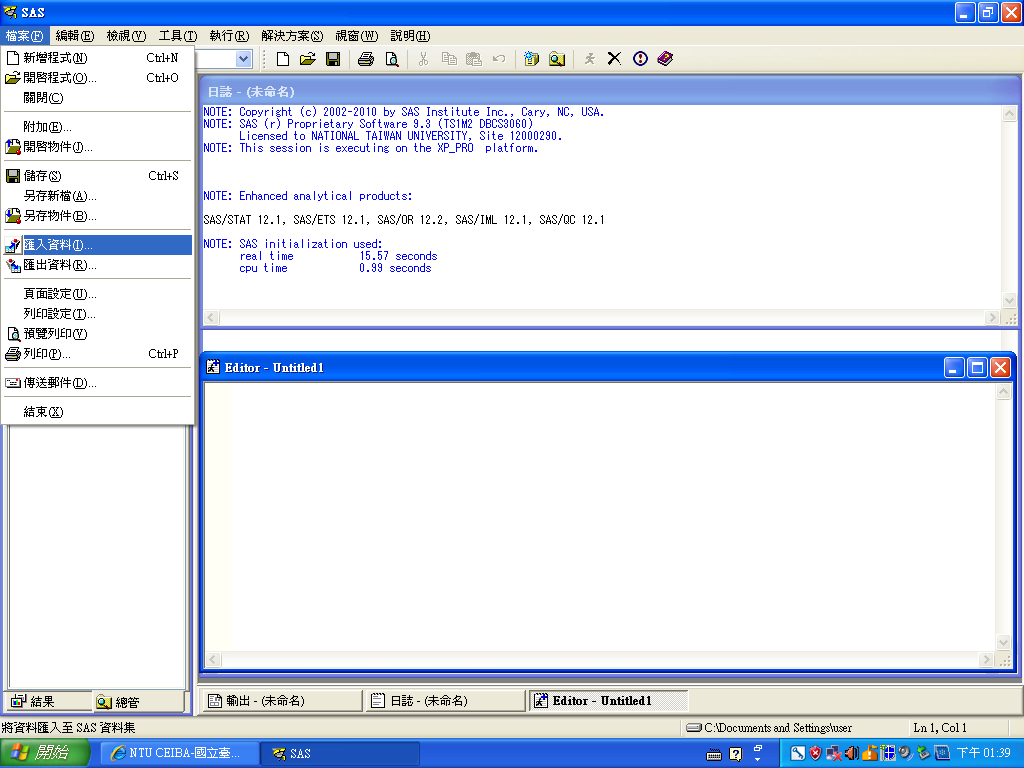

verilog 小整理

wire 型態 電路原件內部資料用,不用output出去的東西 通常用在carry符號:

XOR ^

AND &

OR |

AND 的優先權 > OR

應用:

X Y Z 三個 bit 的sum如何做?

X ^ Y ^ Z

留言

張貼留言