[DSD] Contemporary Logic Design 2/e ch7 筆記

Finite State Machine

Feedback: 將output東西抽回來再送回input

有兩種:positive feedback 跟 negative feedback

Asynchronous sequential logic : state changes occur whenever state input change (elements may be simple wires or delay elements)

Synchronous sequential logic : state changes occur in lock step across all storage elements (using a periodic waveform - the clock)

將下列這個machine是弄成Synchronous !

解法 1 :

解法 2 :

題目:

IN = 1011 1101

求

output : 0101 1110

How to change state diagram to Logic ?

Can any sequential system be represented with a state diagram? Yes !!

Moore machine v.s. Mealy machine

Moore machine:

有state

edge上有input 但沒有把output 標出來

Mealy machine

有state

edge上有input 也有把output標出來

實例:飲料販賣機,要超過 15 cent才open賣飲料!

錢幣:兩個 N = 一個 D , 三個 N (nickel)價值15 cent!

Forward Design

D 跟 T input只有一條線接進去就OK

JK跟SR就需要兩條線來 input

剛剛的賣東西的機器

可以畫成這樣

用兩個D flipflop來implement

都完成後就可以畫出電路!

Feedback: 將output東西抽回來再送回input

有兩種:positive feedback 跟 negative feedback

Asynchronous sequential logic : state changes occur whenever state input change (elements may be simple wires or delay elements)

Synchronous sequential logic : state changes occur in lock step across all storage elements (using a periodic waveform - the clock)

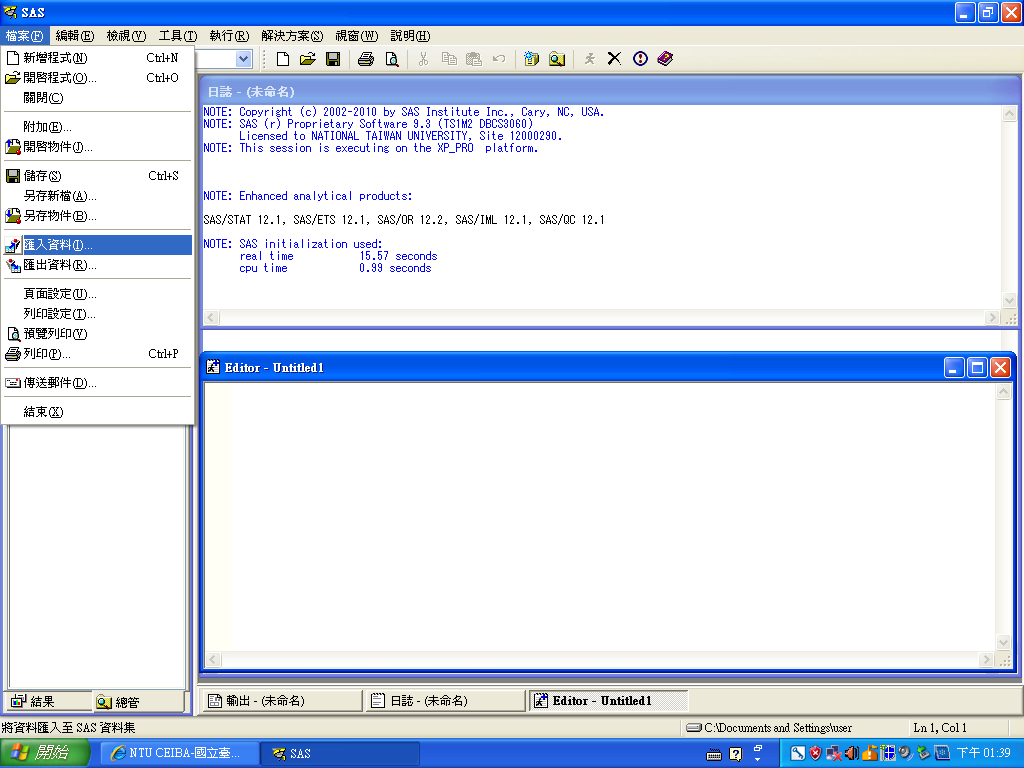

將下列這個machine是弄成Synchronous !

解法 1 :

解法 2 :

題目:

IN = 1011 1101

求

output : 0101 1110

How to change state diagram to Logic ?

Can any sequential system be represented with a state diagram? Yes !!

Moore machine v.s. Mealy machine

Moore machine:

有state

edge上有input 但沒有把output 標出來

Mealy machine

有state

edge上有input 也有把output標出來

實例:飲料販賣機,要超過 15 cent才open賣飲料!

錢幣:兩個 N = 一個 D , 三個 N (nickel)價值15 cent!

Forward Design

D:代表delay

T:代表反向

D flipflop

如果原本Q(t)是0, D是1 ,則等等Q(t+1)就會變1

依此類推!

T 代表反向(Toggle),所以當T是1的時候,Q(t)跟Q(t+1)結果會不一樣!

SR跟JK都代表set 跟 reset

但是SR不允許兩個都是1

而JK兩個都是1的時候就會是 Toggle

這裡的d代表 don't care

JK跟SR就需要兩條線來 input

本表格極為重要

期末務必理解背起來!!

剛剛的賣東西的機器

可以畫成這樣

用兩個D flipflop來implement

利用00, 01, 10, 11

分別到表 0 cent, 5 cent, 10 cent, 15 cent

將上面的表畫成K-map

然後化簡!!

對於D1的k-map與化簡

對於D0的K-map與化簡

都完成後就可以畫出電路!

留言

張貼留言