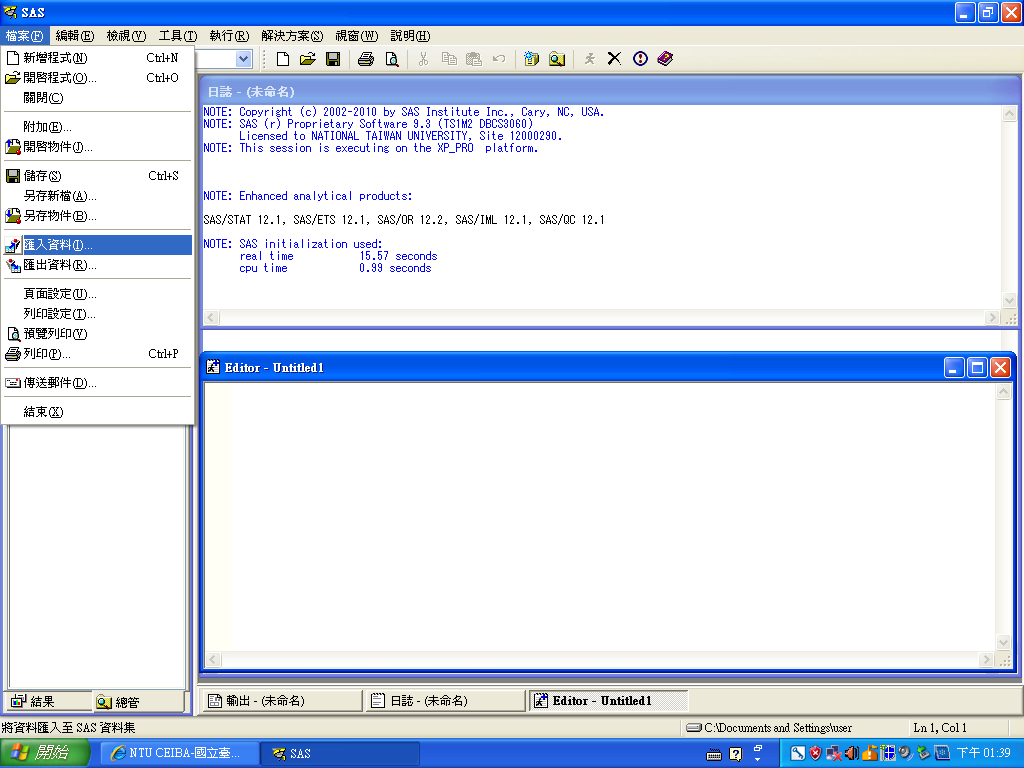

[DSD] Contemporary Logic Design 2/e ch3 筆記

本章重點:

static-1 hazard 與 static-0 hazard 避免方法

由來: 在經過converter時 會有些許delay產生!

static-1 hazard 與 static-0 hazard 與 Dynamic hazard

Static-1 hazard

例

由K-map簡化完之後的Sum of Product (SoP)邏輯電路如圖

解決方法:

看K-Map發現 兩個group之間可以用CD = 01 貫穿!

所以加入 C'D 使得全部變成:F = A'D + AC' + C'D 可以避免掉static-1 hazard

Static-0 hazard

這根剛剛的static-1 hazard 一體兩面,假如真值表出來是寫成

Product of Sum (PoS) form

如圖:

則畫出的邏輯電路會發生 static-0 hazard

要避免的方法同上,發現K-map上面這兩區塊的交集為

CD = 10 也就是CD' --> 以PoS form來表示加入是 (C'+D)

所以加入 C'+D 使得全部變成:F = (A'+C')(A+D)(C'+D) 可以避免掉static-0 hazard

static-1 hazard 與 static-0 hazard 避免方法

由來: 在經過converter時 會有些許delay產生!

static-1 hazard 與 static-0 hazard 與 Dynamic hazard

|

| static-1 hazard: 原本應該要持續 1 的訊號,有一瞬間變成 0 不久又回覆正常 static-0 hazard: 原本應該要持續 0 的訊號,有一瞬間變成 1 不久又回覆正常 |

|

| dynamic hazard: 訊號在 1 與 0 不斷地變動。 |

Static-1 hazard

例

由K-map簡化完之後的Sum of Product (SoP)邏輯電路如圖

|

| 當input 從ABCD=1101變成ABCD=0101時,照理講output要維持著 1 但當A要從1變成0時,會有一瞬間因為A'還沒被改到,而出現A跟A'都是0的情形! 此時導致output在這一瞬間變成了 0 !! 過一下子,A' 順利變成 1 之後,output才回復正常的 1 |

看K-Map發現 兩個group之間可以用CD = 01 貫穿!

所以加入 C'D 使得全部變成:F = A'D + AC' + C'D 可以避免掉static-1 hazard

Static-0 hazard

這根剛剛的static-1 hazard 一體兩面,假如真值表出來是寫成

Product of Sum (PoS) form

如圖:

則畫出的邏輯電路會發生 static-0 hazard

要避免的方法同上,發現K-map上面這兩區塊的交集為

CD = 10 也就是CD' --> 以PoS form來表示加入是 (C'+D)

所以加入 C'+D 使得全部變成:F = (A'+C')(A+D)(C'+D) 可以避免掉static-0 hazard

留言

張貼留言