[DSD] Contemporary Logic Design 2/e ch4 筆記

PLAs and PALs

s代表邏輯

PLA: Programmable Logic Array

PAL: Programmable Array Logic

(PLAs 跟 PALs 基本上是指同樣的東西,只是,PAL會有資源上的限制,

像是限制使用的OR GET數量以及形式。)

例:

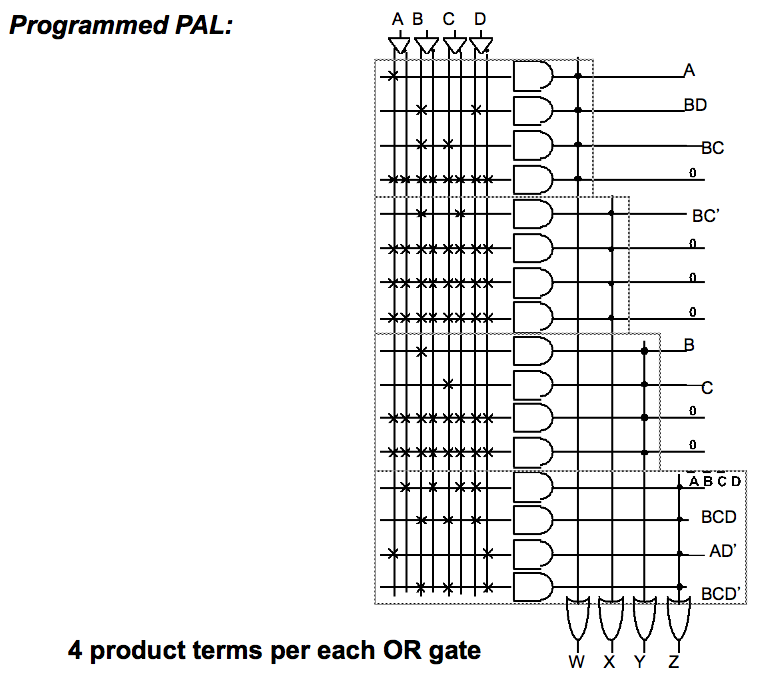

例:將此真值表的線路圖畫出!

input : A, B, C, D

output: W, X, Y, Z

首先,先用K-map來簡化

簡化後,再用PALs來畫,這裡的OR get有限制,四個一組!

完成!

Verilog 語法 - 變數宣告

wire a; //純量變數

wire [7:0] bus; //8-bit

wire [31:0] busA,busB,busC; // 3個32-bit

wire [40:0]

b 二進位,h 十六進位,o八進位,d十進位

4'b1111 // 4-bit 二進位數 1111

12'habc // 12-bit 十六進位數 abc

16'd255 // 16-bit 十進位數 255

x - 不確定的值

A = 11' hx

reg signed [3:0] j

Array

integer count [0:7] ; // 8個整數組成的陣列

~ not

{} 用來將不同信號組合在一起

C[10:0] = {a[2,0] , 4'b1101, a[3], 1'b1, 1'b0 }

a的最後三個bit 再接 1101 再接a的array號碼3那個bit 再接1 0

module add(a,b,ci,sum)

...

...

...

endmodule

括號裡面一定要有所有的input output變數

判斷式

跟C一模一樣

{ } 用 begin 跟 end 取代

特殊字:

initial

always

s代表邏輯

PLA: Programmable Logic Array

PAL: Programmable Array Logic

(PLAs 跟 PALs 基本上是指同樣的東西,只是,PAL會有資源上的限制,

像是限制使用的OR GET數量以及形式。)

|

| 先經過AND GET,再經過OR GET,最後的ouput為Sum of Products(SoP)型式 |

例:

|

PLAs 跟 PALs 基本上是指同樣的東西,只是,PAL會有資源上的限制,

像是限制使用的OR GET數量以及形式。

|

例:將此真值表的線路圖畫出!

input : A, B, C, D

output: W, X, Y, Z

首先,先用K-map來簡化

簡化後,再用PALs來畫,這裡的OR get有限制,四個一組!

完成!

Verilog 語法 - 變數宣告

wire a; //純量變數

wire [7:0] bus; //8-bit

wire [31:0] busA,busB,busC; // 3個32-bit

wire [40:0]

b 二進位,h 十六進位,o八進位,d十進位

4'b1111 // 4-bit 二進位數 1111

12'habc // 12-bit 十六進位數 abc

16'd255 // 16-bit 十進位數 255

x - 不確定的值

A = 11' hx

reg signed [3:0] j

Array

integer count [0:7] ; // 8個整數組成的陣列

~ not

{} 用來將不同信號組合在一起

C[10:0] = {a[2,0] , 4'b1101, a[3], 1'b1, 1'b0 }

a的最後三個bit 再接 1101 再接a的array號碼3那個bit 再接1 0

module add(a,b,ci,sum)

...

...

...

endmodule

括號裡面一定要有所有的input output變數

判斷式

跟C一模一樣

{ } 用 begin 跟 end 取代

特殊字:

initial

always

留言

張貼留言